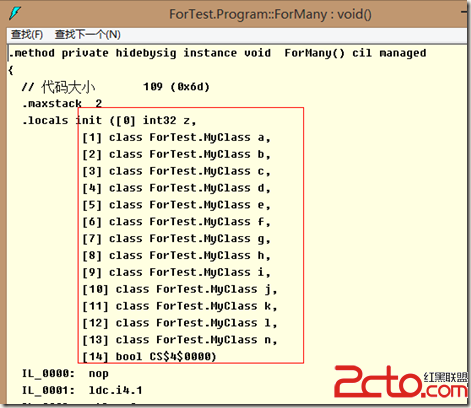

source code

以ARM926EJ-S为例分析,

主要的代码位于arch/arm/mm/cache-arm926.s和arch/arm/mm/proc-arm926.s

1. cache和tlb的定义

#ifdef MULTI_CACHE

ENTRY(\name\()_cache_fns)

.long \name\()_flush_icache_all

.long \name\()_flush_kern_cache_all

.long \name\()_flush_user_cache_all

.long \name\()_flush_user_cache_range

.long \name\()_coherent_kern_range

.long \name\()_coherent_user_range

.long \name\()_flush_kern_dcache_area

.long \name\()_dma_map_area

.long \name\()_dma_unmap_area

.long \name\()_dma_inv_range

.long \name\()_dma_clean_range

.long \name\()_dma_flush_range

.size \name\()_cache_fns, . - \name\()_cache_fns

.endm

/*

* thecache line size of the I and D cache

*/

#define CACHE_DLINESIZE 32

/*

* MM Cache Management

* ===================

*

* The arch/arm/mm/cache-*.S andarch/arm/mm/proc-*.S files

* implement these methods.

*

* Start addresses are inclusive and endaddresses are exclusive;

* start addresses should be rounded down,end addresses up.

*

* See Documentation/cachetlb.txt for moreinformation.

* Please note that the implementation ofthese, and the required

* effects are cache-type (VIVT/VIPT/PIPT)specific.

*

* flush_icache_all()

*

* Unconditionally clean andinvalidate the entire icache.

* Currently only needed forcache-v6.S and cache-v7.S, see

* __flush_icache_all for thegeneric implementation.

*

* flush_kern_all()

*

* Unconditionally clean andinvalidate the entire cache.

*

* flush_user_all()

*

* Clean and invalidate all userspace cache entries

* before a change of pagetables.

*

* flush_user_range(start, end, flags)

*

* Clean and invalidate arange of cache entries in the

* specified address spacebefore a change of page tables.

* - start - user startaddress (inclusive, page aligned)

* - end - user end address (exclusive, page aligned)

* - flags - vma->vm_flagsfield

*

* coherent_kern_range(start, end)

*

* Ensure coherency betweenthe Icache and the Dcache in the

* region described by start, end. If you have non-snooping

* Harvard caches, you need toimplement this function.

* - start - virtual start address

* - end - virtual end address

*

* coherent_user_range(start, end)

*

* Ensure coherency betweenthe Icache and the Dcache in the

* region described by start,end. If you have non-snooping

* Harvard caches, you need toimplement this function.

* - start - virtual start address

* - end - virtual end address

*

* flush_kern_dcache_area(kaddr, size)

*

* Ensure that the data heldin page is written back.

* - kaddr - page address

* - size - region size

*

* DMA Cache Coherency

* ===================

*

* dma_inv_range(start, end)

*

* Invalidate (discard) thespecified virtual address range.

* May not write back anyentries. If 'start' or 'end'

* are not cache line aligned,those lines must be written

* back.

* - start - virtual start address

* - end - virtual end address

*

* dma_clean_range(start, end)

*